Hello everyone,

I am using the latest version of the xilinx mpsoc zcu102 development board and i am trying to create a barematal application that uses the AXI DMA on the programmable logic, using the scatter gather example from the xilinx repository. This works perfectly

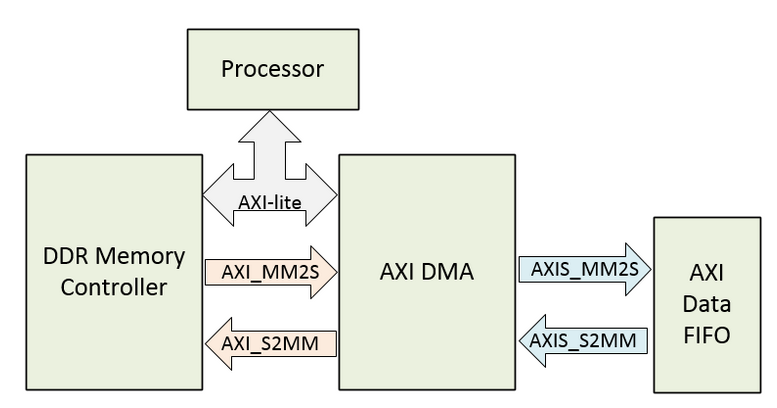

well for the baremetal application. The diagram below represents the information flow. The AXI DMA and the AXI data FIFO are in the Programable logic (FPGA). This AXI DMA is out of the box IP from Vivado and uses a single channel (Does not use AxUSER) which

means the AXI ID cannot manually be set.

Now i want to make this as a baremetal hypervisor guest, in future this will be replaced by a custom IP with cache colouring enabled. I want to pass through the AXI DMA in the PL. (Not to be used by Dom0)

I followed this tutorial

Baremetal

+ DomU guest changed the base address to 0x4000000,(1GB allocated to Dom-0) to create my EL1 binary. I used Petalinux 2020.2 to generate my linux, xen image and use tftp to boot.

From what i understand from the xilinx tutorials

Xen+and+PL+Masters section 3 and

MPSOC SMMU section 4, stream ids are required by the SMMU to get the correct address translation.

I am still unable to figure out how to get the iommu property for my AXI DMA and how to set the dtdev config for my hypervisor guest.

I can also see some new updates with the XEN 2020.1 and 2020.2 releases which i can be useful to my application

I would really appreciate if someone can help me with a way forward or elaborate on the above updates or provide an example guest config file.

Please find attached my .dtsi files generated from petalinux.

Best Regards,

Prem