# arm

## Xen on the Arm<sup>®</sup> RD-1 AE

Running Xen on the latest Arm Automotive platform design

Luca Fancellu 24/10/2024

© 2024 Arm

#### Outline

- Introduction to the RD-1 AE platform

- Software architecture

- Xen on RD-1 AE

- Heterogeneous Inter-Processor Communication

- Network topology

- Arm features in Xen

- GICv4.1 + PCI passthrough

- MPAM

- SVE

- Testing

- Links

#### Introduction to the RD-1 AE

- The Arm Reference Design-1 AE, or RD-1 AE introduces few concept:

- Primary Compute

- High-performance Arm<sup>®</sup> Neoverse<sup>™</sup> V3AE Application Processors (Armv9.2-A)

- Safety Island

- 3 clusters of Arm<sup>®</sup> Cortex<sup>®</sup>-R82AE (Armv8-R AArch64)

- Runtime Security Engine (RSE)

- Cortex-M55 (Armv8.1-M)

- A Fixed Virtual Platform (FVP) is available as part of the Reference Design.

- https://developer.arm.com/downloads/-/arm-ecosystem-fvps

#### Software architecture

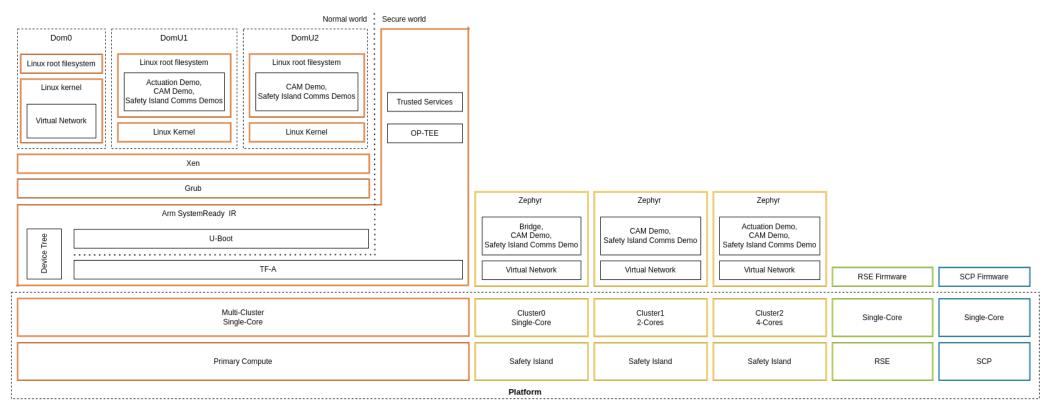

- The SW stack implements a Baremetal and a Virtualization Architecture

- Focus on the Virtualization Architecture

#### Arm Automotive Solutions High-Level Diagram - Virtualization Architecture

#### Xen on RD-1 AE

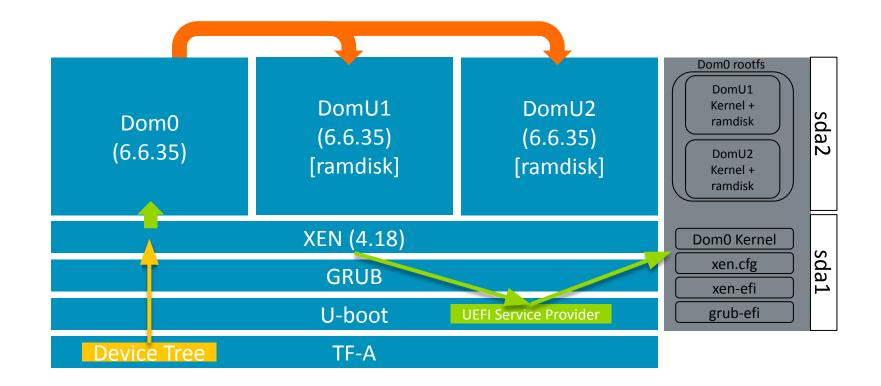

- Xen is started by the U-boot -> GRUB chain

- UEFI Xen stub uses the UEFI provider to read the disk and load Dom0 Kernel

- Once the Dom0 Kernel is started, DomU1 and DomU2 are started using XL

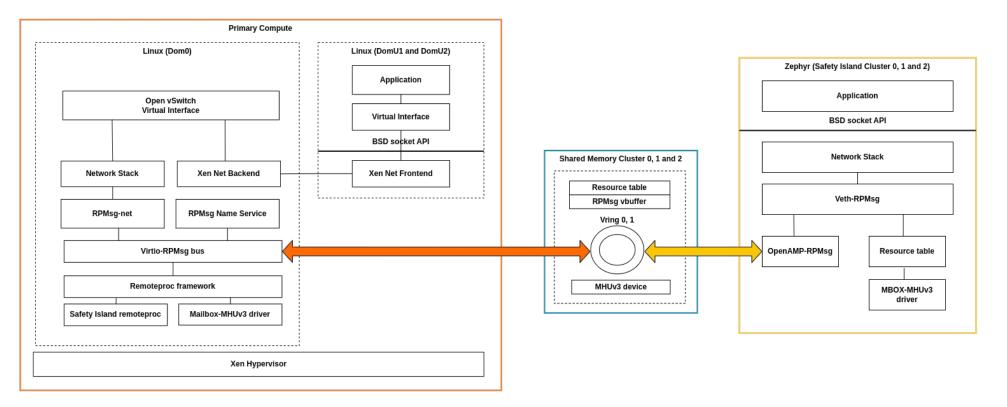

#### Xen on RD-1 AE - HIPC

- Custom Linux driver for Heterogeneous Inter-Processor Communication for DomO:

- DomU1 and DomU2 uses PV network drivers

Arm Automotive Solutions HIPC - Virtualization Architecture

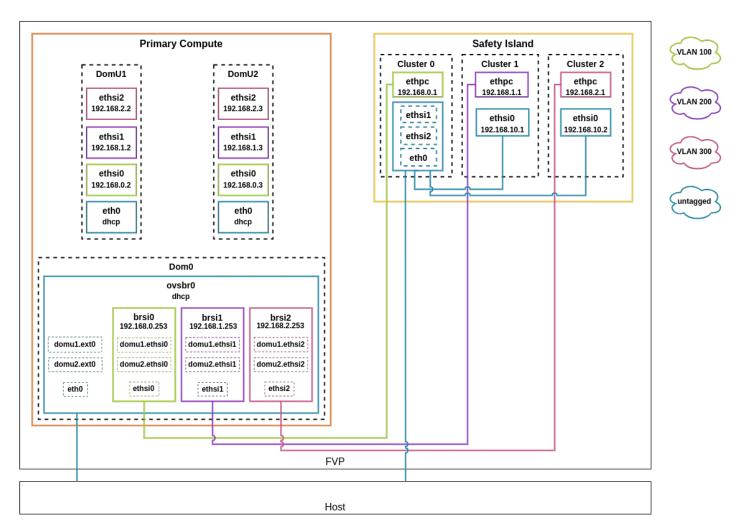

### Xen on RD-1 AE – Network Topology

- Dom0 runs Open vSwitch:

- Network bridges

- VLAN traffic

- Safety Island Clusters have different VLAN IDs

- Ethsi<X> and eth0 are for development purpose only

- Every DomU can reach every cluster, but depending on the use-case it can be restricted

Arm Automotive Solutions Network Topology - Virtualization Architecture

### Arm features in Xen

- **MPAM**

- Provide MPAM support for the System Level Cache (L3) partitioning

- Dom0 has ¼ of the available SLC portions

- DomU1 and DomU2 has 1/8 respectively of the available SLC portions

- Partitions are for demonstration purpose only

- GICv4.1 + PCI Passthrough

- DomU1 has a PCI AHCI SATA Disk attached to it

- SVE/SVE2

- The Neoverse<sup>TM</sup> V3AE Application Processors is SVE/SVE2 capable, <sup>root@domu1:~# cat /proc/sys/abi/sve\_default\_vector\_length</sup> Dom0 and the guests can use SVE/SVE2 instructions

- Maximum vector length is 128 bit (16 byte)

| Socket ID    | 0        |      |

|--------------|----------|------|

| SLC          | 32768KB  |      |

| Default CPBM | Øxffff   |      |

| ID           | NAME     | CPBM |

| 0            | Domain-0 | Øxf  |

| 1            | domu1    | Øxce |

| 2            | domu2    | 0x30 |

#### Testing

- The SW stack is built using Yocto, the testing is performed using Yocto OEQA

- Based on Python unittest

- Performs tests on the FVP platform

- Uses Pexpect library to interact with the platform

- Testing examples:

- Test case that checks Dom0 has boot to shell, performs the login and uses xl console <dom> to test that the DomUs reaches the prompt and the shell.

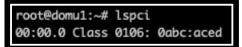

- Test case that checks PCI Passthrough is working correctly, starting the system, checking that DomU1 sees the disk (lspci)

- Test case that checks GICv4.1 vLPI direct injection is working correctly, looking into /proc/interrupts for non-zero MSI-X/IPI0 interrupts

- Test case that uses BATS in order to validate MPAM configuration is applied on boot and after guests lifecycle management.

#### Links

- The SW stack can be browsed at:

- <u>https://gitlab.arm.com/automotive-and-industrial/arm-auto-solutions/sw-ref-stack</u>

- The SW stack documentation can be found at:

- <u>https://arm-auto-solutions.docs.arm.com/</u>

|            | + |  |  |  |  |                             |  |

|------------|---|--|--|--|--|-----------------------------|--|

| arr        |   |  |  |  |  | Thank You<br>+ Danke        |  |

|            |   |  |  |  |  | Gracias                     |  |

|            |   |  |  |  |  | → Grazie<br>谢谢              |  |

|            |   |  |  |  |  | ありがとう<br>Asante             |  |

|            |   |  |  |  |  | Merci<br>감사합니다              |  |

|            |   |  |  |  |  | धन्यवाद<br>+ Kiitos         |  |

|            |   |  |  |  |  | شکرًا<br>ধন্যবাদ            |  |

| © 2024 Arm |   |  |  |  |  | <b>౧౹౹ఀ౧</b><br>ధన్యవాదములు |  |

|            |   |  |  |  |  |                             |  |

arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks

| © 2024 Arm |  |  |  |  |  |  |

|------------|--|--|--|--|--|--|

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |